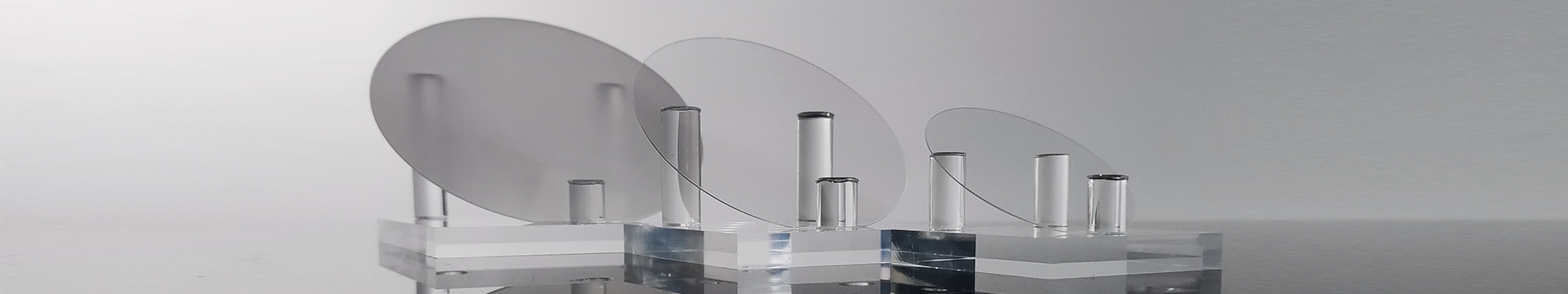

As the semiconductor industry moves towards the "post-Moore era", advanced packaging has become a core path to sustain chip performance improvement and achieve high-density integration. With its unique physical, chemical and electrical properties, glass wafers are gradually replacing traditional silicon substrates and organic substrates, becoming a key core material in advanced packaging processes. They run through the entire packaging process and support the implementation of cutting-edge technologies such as 2.5D/3D integration and Chiplet stacking. Their roles are mainly reflected in several core dimensions including interconnection support, performance optimization and scenario adaptation, as detailed below:

I. Core Interconnection Carrier: Building Efficient 3D Vertical Interconnection Channels

Through Through Glass Via (TGV) technology,

glass wafers establish vertical electrical interconnections between chips and chips, and between chips and substrates, serving as the core support for 3D integration in advanced packaging, which is also their most core role. TGVs are microvias (usually 10μm-100μm in diameter) passing through glass wafers, which are metallized through processes such as seed layer sputtering, electroplating filling and chemical mechanical planarization. Each wafer can integrate tens of thousands of TGVs to form a high-density interconnection network, providing key connection guarantees for Chiplet stacking and multi-chip integration.

Compared with traditional Through Silicon Vias (TSV), the TGV technology of glass wafers has significant advantages: on the one hand, glass has excellent insulation performance, which can effectively avoid signal crosstalk and reduce insertion loss, making it particularly suitable for high-frequency signal transmission and providing reliable interconnection solutions for scenarios such as radio frequency (RF) components and Co-Packaged Optics (CPO); on the other hand, TGVs can achieve closer via spacing (Intel has achieved spacing within 100μm), increasing interconnection density by 10 times, while supporting thinner wafer thickness (50µm-100µm), helping to miniaturize and compact the packaging structure and lay the foundation for integrating more Chiplets in a single package. Intel stated that its glass substrate technology can increase the chip area in a single package by 50%, helping to achieve the goal of 1 trillion transistors per package by 2030.

II. Precision Support and Bearing: Ensuring the Stability of Packaging Processes

Advanced packaging has extremely high requirements for substrate flatness, dimensional stability and mechanical strength. With its excellent physical properties, glass wafers assume the key role of chip bearing and process support, solving many pain points of traditional substrates.

In terms of flatness, the surface of glass wafers is extremely smooth (roughness less than 1nm), enabling line width/spacing below 2 microns, greatly improving the lithography accuracy of the Redistribution Layer (RDL), providing guarantee for fine wiring, and avoiding bonding defects caused by surface unevenness. In terms of dimensional stability, the Coefficient of Thermal Expansion (CTE) of glass can be precisely adjusted to 3-5 ppm/°C, which is highly matched with silicon chips (2.6 ppm/°C), significantly reducing thermal stress during multi-chip stacking and high-temperature packaging, and reducing substrate warpage. Intel tests show that the high-temperature warpage of glass substrates is more than 70% less than that of organic substrates, and Samsung's T-glass substrate even reduces the CTE by 50%, effectively avoiding problems such as chip detachment and interconnection failure.

In addition,

glass wafers have high chemical resistance, chemical inertness and good mechanical stability, which can withstand complex processes such as etching, electroplating and high-temperature baking in the packaging process. At the same time, their customizable thickness (50µm to 900μm) and large-size panel form (up to over 2m×2m) can adapt to different packaging scenario needs, providing stable bearing support from 6-inch, 12-inch wafers to large-scale panel-level packaging.

III. Performance Optimization and Empowerment: Improving the Overall Efficiency of Chip Packaging

The inherent properties of glass wafers not only solve the performance bottlenecks of traditional substrates, but also empower chip packaging from electrical, heat dissipation and cost dimensions, promoting the evolution of packaging technology towards higher performance, lower power consumption and lower cost.

In terms of electrical performance, glass has a low Dielectric Constant (Dk) and low Dissipation Factor (Df), making it an ideal electrical insulator, which can significantly reduce signal transmission loss and delay, especially suitable for high-frequency and high-speed scenarios. In fields such as 6G communication, RF modules and AI chips, the low-loss characteristics of glass wafers can significantly improve signal integrity, helping chips achieve higher computing power and faster response speed. At the same time, the high transparency and low fluorescence of glass facilitate optical alignment and detection during the packaging process, improving process yield.

In terms of heat dissipation and power consumption,

glass substrates have excellent thermal stability, which can seamlessly embed optical interconnections, capacitors, inductors and other devices, optimizing power supply and signal transmission rules. At the same time, their good heat dissipation characteristics are suitable for high-power device packaging. In scenarios such as data center AI servers and high-computing-power chips, they can effectively reduce device power consumption and improve operational stability. In terms of cost control, although the current cost of glass wafers is relatively high, large-size panel-level manufacturing (such as 600×600mm) can greatly improve material utilization (TSMC's CoPoS technology increases material utilization to more than 90%). Combined with the recyclable and reusable characteristics of glass wafers, the packaging cost per chip is expected to be reduced by 30%-40% compared with traditional technologies after large-scale mass production.

IV. Scenario Adaptation and Expansion: Supporting High-End Packaging Needs in Multiple Fields

With the rapid development of fields such as AI, HPC, autonomous driving and CIS, the demand for packaging technology in different scenarios is differentiated. With its customizable characteristics, glass wafers adapt to a variety of high-end packaging scenarios and become a key material for promoting technological breakthroughs in segmented fields.

In the AI and HPC fields, glass wafers support ultra-large-size SiP packaging (such as Intel's planned 24×24cm SiP), which can accommodate more Chiplets to meet the integration needs of high-computing-power chips. Giants such as TSMC, Intel and Samsung all regard it as the core solution for AI chip packaging: TSMC's CoPoS technology focuses on large-scale cost reduction, adapting to massive needs such as NVIDIA GPUs; Intel focuses on extreme stability to support trillion-transistor CPUs; Samsung focuses on customization, providing high-end solutions for customers such as Apple and Broadcom.

In the field of RF and analog circuits, the low-loss and high-stiffness characteristics of glass wafers make them ideal substrates for integrating passive devices, solving the pain points of high loss and high process cost of silicon-based substrates, and adapting to scenarios such as RF modules and automotive camera modules. In the field of MEMS and CIS,

glass wafers can be used as capping wafers, providing vertical connections through TGV technology to ensure the service life and reliability of sensors, and their high transparency can adapt to the packaging needs of optical sensors. In addition, in HBM memory packaging, glass wafers improve signal integrity and warpage control capabilities through multiple bonding, ultra-flat carrier and other technologies, becoming one of the fastest-growing application directions in this field.

V. Industrial Upgrade Support: Promoting Breakthroughs in Advanced Packaging Technology

The application of

glass wafers is not only a material replacement, but also promotes the iterative upgrading of advanced packaging technology, providing key support for "More than Moore". Traditional organic substrates (such as FR-4) have limitations such as high-temperature warpage, low wiring density and high high-frequency loss, which can no longer meet the needs of high-density integration. The emergence of glass wafers breaks the technical bottlenecks of

silicon substrates and organic substrates, promoting the upgrading of packaging technology from 2D to 3D integration and from wafer-level to panel-level.

At present, glass wafer-related technologies have entered a critical stage of transition from laboratory to mass production, and 2026-2030 will be a critical window for their commercial landing. Enterprises such as Corning, Asahi Glass and Schott continue to make breakthroughs in low-warpage and ultra-thin glass materials. Semiconductor giants such as Intel, Samsung and TSMC have successively laid out production capacity to promote the maturity of TGV technology and panel-level packaging technology. As a core material, the continuous optimization of performance and cost reduction of

glass wafers will further accelerate the popularization of advanced packaging and help the semiconductor industry achieve "overtaking on curves".

In summary, in advanced semiconductor packaging processes,

glass wafers are not only the core carrier for building high-density interconnections, but also the precision support for ensuring process stability, and even the key enabler for optimizing packaging performance and expanding application scenarios. Their wide application will promote the semiconductor industry towards higher integration, higher performance and lower cost, becoming one of the core materials in the semiconductor industry in the post-Moore era.